从外部RAM运行图形

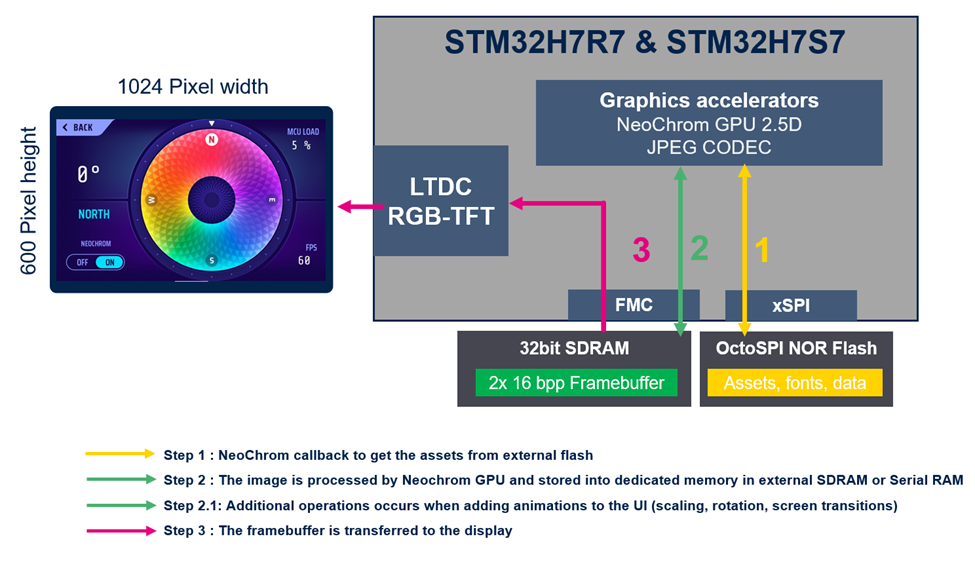

本节介绍如何计算下图所示典型配置的图形性能。 示例采用1024x600像素的高分辨率24位RGB-TFT显示屏,帧缓存为16bpp格式并存储于外部32位SDRAM中。 图形资源存储在外部OSPI NOR Flash中。

目标

- 为开发人员提供分步指导,帮助其更好地理解和评估图形用户界面应用的系统性能。

- 验证所选显示屏及其需求是否能在指定系统配置下持续运行。

- 明确在定义的子系统范围内可开发何种复杂程度的GUI。

步骤1:显示屏规格

STM32H7S78探索套件采用的显示屏型号为MB1860。 探索套件的BOM链接见此处。 探索套件显示屏的分辨率为800×480像素,低于本例中的配置。 本例的显示屏规格如下:

- 显示高度:600 px

- 显示宽度:1024 px

- 显示器刷新率:60 Hz

- 显示消隐区占比*:通常约10%

*显示消隐区包含所有非活跃像素。 主要由LTDC的 porch区域构成。

步骤2:显示屏需求与像素时钟计算

本步骤需计算显示需求,以确认所选MCU和存储器能否满足显示规格要求。

根据上述分辨率,总像素数为:

像素高度 × 像素宽度 = 600 px × 1024 px = 614400 px

显示屏刷新率为60Hz (1000ms/60 = 16 ms),因此LTDC需要每16ms从帧缓存读取数据并发送至显示屏。 不考虑消隐区时,维持60 Hz刷新所需的系统 (RAM) 带宽可通过以下公式计算:

总像素数 × 刷新率 × 帧缓存色深 (RGB565)

614,400 px × 60 Hz × 16 bpp = 589,824,000 bit/s = 589.82 Mbps

60Hz 刷新率所需的像素时钟频率计算如下:

(总像素数 × 刷新率 × (消隐区占比% / 100 + 1))/ 1000000

(614400 px × 60 Hz × (10 / 100 + 1)) / 1000000 = 40.55 MHz像素时钟

Caution

像素时钟不得超过LTDC支持的最大值。 有关不同配置下最大像素时钟的概述,请查阅[LTDC应用笔记AN4861] (https://www.st.com/resource/zh/application_note/an4861-lcdtft-display-controller-ltdc-on-stm32-mcus-stmicroelectronics.pdf)。 STM32H7R/S的最大像素时钟详情请参见表13。

STM32H7R/S支持的最大像素时钟详见下方插入的LTDC应用笔记表13。

步骤3:帧缓存和存储器策略

本例采用32位宽FMC接口连接外部32位SDRAM,运行频率为100 MHz,并采用双帧缓存策略。 此外,开发人员还可选用16位SDRAM或200MHz DTR模式的4/8/16位串行RAM(如Hyper RAM和串行PSRAM)。

所有外部存储器均需额外周期启动操作,本例假设SDRAM效率约为80%。

步骤4:帧缓存性能

当前后缓存位于不同RAM库时,理论RAM吞吐量公式为:

接口位宽 × 接口频率 = Mbit/s

32 bit × 100 MHz = 3200 Mbps = 400 MB/s

然而,此吞吐量是基于RAM以100%的效率运作的假设。 若考虑步骤3中的估计效率,实际吞吐量为:

3200 Mbps × 0.8 = 2560 Mbps = 320 Mbyte/s

步骤5:计算显示更新后的剩余带宽

前文可知显示屏需要589.82 Mbps带宽,而外部RAM吞吐量为2560 Mbps。 现在让我们计算可用于屏幕渲染/动画的剩余带宽。

2560 Mbps - 589.82 Mbps = 1970.18 Mbps = 246.27 MByte/s

总体而言,示例系统在维持显示更新的同时,还可为额外动画和UI图层提供约1970 Mbps剩余带宽。

步骤6:UI渲染性能(GUI 帧率)

在此UI用例中,我们的目标是实现60FPS的GUI渲染。 这意味着系统必须在16 ms内渲染并传输新帧。 此外,对于某些高级UI动画可接受帧率降至30FPS,以确保整体流畅的用户体验。

让我们计算每帧缓存片的性能,即每帧(每16 ms)可渲染的数据量。 首先取剩余帧缓存带宽1970 Mbps除以60FPS。

1970 Mbps / 60FPS = 每帧32.8 Mbps(60FPS约16 ms)。

计算结果表明,系统需在每16 ms周期内完成32.8 Mbps的数据吞吐,以满足UI的实时渲染和更新需求。

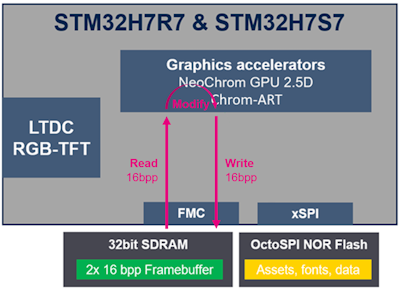

初始配置图示的步骤2展示了用于修改/更新UI的额外渲染流程。 由于帧缓存采用16 bpp格式,所有帧缓存操作均以16 bpp执行。 因此在帧缓存中写入单个像素将占用16位SDRAM带宽。 若需混合像素,NeoChrom GPU将首先从帧缓存读取该像素。 完成像素混合(修改)后再写回帧缓存。 这意味着系统执行读取-修改-写入操作需传输两次16位数据,共占用32位SDRAM带宽(16位读取 + 16位写入),如下图所示。

基于此,可计算单帧周期内可处理的像素数量:

32.8 Mbps/帧/ 16 bpp = 205万像素

为提供直观参考,进一步计算单帧周期内可完成的全屏操作次数:

205万像素/ 614000像素 = 3.34次

这意味着系统可以先绘制全屏色块,再与第二个色块混合(16 bpp写入+ 16 bpp读取+ 16 bpp写入)。 然后进一步与覆盖17%屏幕的第三色块混合(34%带宽/2)。

如步骤6开头所述,部分高级UI动画可接受帧率降至30FPS。 这意味着相比60FPS,可用带宽翻倍,单帧全屏操作次数可提升至:

3.34 × 2 = 6.68次

单帧可执行的全屏操作次数无法一概而论,这很大程度上取决于UI的复杂程度。 此外需考虑外部RAM是否需用于帧缓存之外的其他用途。 但对多数应用而言,合理的基准应保持3次以上全屏操作能力。

STM32H7S78-DK开发板采用800×480分辨率的RGB TFT显示屏,其16位帧缓存存储于外部16位串行PSRAM中,工作于200MHz双倍传输速率 (DTR) 模式,理论传输带宽可达800 MB/s(工作效率100%时)。 相较于SDRAM,该串行PSRAM在初始化阶段需要更多时钟周期,导致内存初始化效率较低(有关串行RAM性能的详细信息,请参见AN6062)。 上述示例和计算表明,在此分辨率下,系统完全能够支持复杂UI的实时渲染,并稳定保持60FPS的刷新率性能。

TouchGFX Demo提供了另一个典型参考案例,其复杂UI支持RAM和Flash存储器的双频工作模式配置。

Further reading

注意

需注意,上述计算仅基于RAM带宽分析,未考虑实际可用计算能力。 同时,相关计算结果建立在RAM效率假设基础上。 尽管这些假设有依据,但仍属于理论范畴。

尽管存在局限性,本示例中的分析方法仍可为性能评估提供有效参考。

词汇表

- 读取-修改-写入:读取内存数据、修改、写回的操作过程。

- 像素时钟:像素传输到显示器的频率,决定屏幕的刷新率和分辨率。 即显示控制器向面板发送像素数据的速度。

- 帧缓存:存储显示位图的RAM区域。 显示控制器从中读取像素值。 所有渲染操作均作用于该区域。

- 消隐区:显示无效像素的总和。 主要由LTDC的 porch区域构成。

- FMC:可变存储控制器。 管理CPU与各类存储器(如SRAM、NOR、NAND和SDRAM)之间接口的硬件组件。 本例中用于控制外部SDRAM。

- XSPI:扩展SPI接口。 SPI的高级版本,支持更高的数据传输速率及增强外设通信功能。 本例中用于连接外部NOR Flash。 详见wiki说明。

- 存储器协议开销:管理内存与处理器之间的通信和数据传输所需的额外时间和资源,包括错误校验、握手协议和寻址等任务。 这种开销会影响系统的整体性能。

- DTR:双倍传输速率。 数据在时钟上升沿和下降沿传输。 从而实现带宽倍增。