ディスプレイ

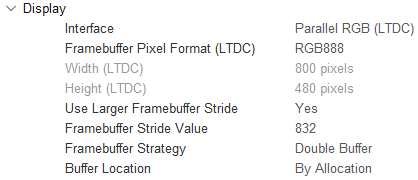

Displayグループには、ディスプレイに関連する設定(インタフェース、寸法、バッファリング戦略など)が含まれます。

インタフェースと寸法

現在、STM32マイクロコントローラでは、次に示すような複数のディスプレイ・インタフェースを使用できます。

- パラレルRGB(LTDC)

- MIPI DSI

- FMC

- SPI

ディスプレイがLTDCまたはFMCのインタフェースで接続されたマイクロコントローラの場合、TouchGFX Generatorは、接続されたディスプレイにフレームバッファを転送するためのコードを生成できます。 DSIおよびSPIインタフェースのドライバは、開発者自身で実装する必要があります。

Further reading

フレームバッファのピクセル・フォーマット

TouchGFX Generatorによって、以下のフレームバッファのピクセル・フォーマットが現在サポートされています。 Customディスプレイ・インタフェースを使用する場合はすべてのオプションを使用できます。それ以外の場合、オプションはディスプレイ・コントローラの設定に制限されます(たとえば、LTDCフレームバッファの形式を「RGB565」に設定すると、TouchGFX Generatorのオプションは「RGB565」に制限されます)。

- BW(1bpp)

- Grey2(2bpp)

- Grey4(4bpp)

- ABRG2222(8bpp)

- ARGB2222(8bpp)

- BGRA2222(8bpp)

- RGBA2222(8bpp)

- RGB565(16bpp)

- RGB888(24bpp)

- ARGB8888(32bpp)

- XRGB8888(32bpp)

Note

フレームバッファのストライド

ディスプレイの実際の幅よりもフレームバッファのストライドが大きい一部のディスプレイ・インタフェース(MIPI-DSIなど)では、より大きなストライドがデータ・パケット・サイズとよりよく整合している場合に、ディスプレイへのデータ転送速度が向上する可能性があります。 より大きなフレームバッファのストライドを使用する場合、以下のような設定が可能です。

- No - フレームバッファのストライドとディスプレイの幅が同じサイズです。

- Yes - ユーザがフレームバッファのストライド長を指定できます。

バッファリング戦略とロケーション

TouchGFX Generatorを介して、次のフレームバッファ戦略を設定できます。

- Single Buffer - アプリケーション・フレームバッファを1つだけ使用します。 パフォーマンスが制限される可能性がありますが、メモリの使用量は少なくて済みます。 [Buffer Location]設定で使用して、内部RAMに配置します。 さらに最適化するには、ディスプレイ・コントローラによって現在処理されているラインを返す関数をユーザが定義できます。 このメソッドはフレームワークによって使用され、このフレーム中にすでにディスプレイに転送済みのメモリへの更新ができるようになります。

- Double Buffer - 2つのフレームバッファを使用します。 通常、多くのメモリを必要としますが、パフォーマンスが向上します。

- Partial Buffer - GRAMディスプレイ - 1つ以上のユーザ定義のメモリ領域をフレームバッファとして使用し、バッファ内のデータがディスプレイのGRAMに転送されます。 この戦略は外部RAMに頼らないが、ディスプレイのフレームバッファ全体では使用可能なメモリ量を超える可能性がある場合の低コストのソリューションをターゲットにしています。

- Partial Buffer - LTDC駆動ディスプレイ - ディスプレイ・サイズの2のべき乗の分数(1/2、1/4、1/8など)で表される単一のメモリ・ブロックを使用します。 この戦略は、外部RAMや大きなディスプレイ解像度を持たないプラットフォームを対象とします。 この戦略にはLTDC駆動ディスプレイとGFXMMUが必要です。

シングル・バッファ、ダブル・バッファ、パーシャル・バッファ - LTDC駆動ディスプレイの場合、ユーザは[Buffer Location]設定で次のオプションを使用して場所を設定します。

- By Allocation - リンカがリンカ・スクリプトに従ってフレームバッファのメモリを配置します。 デフォルトは内部RAMです。

- By Address - ユーザが1つ(シングル)または2つ(ダブル)のフレームバッファ・アドレスを定義できます。

パーシャル・バッファ - GRAMディスプレイ戦略では、ユーザは以下のパラメータを定義します。

- ブロック数(常に内部RAMに配置される)

- ブロック・サイズ(バイト)

パーシャル・バッファ - LTDC駆動ディスプレイ戦略では、ユーザは以下のパラメータを定義します。

- パーシャル・ブロックの数(デフォルトは4で、フレームバッファ・ブロックがディスプレイ・サイズの1/4であることを意味します)

フレームバッファ戦略に関する主要な概念を理解するには、「フレームバッファ戦略」の記事を参照してください。

以下のいくつかのシナリオでは、各種ディスプレイ・インタフェースやフレームバッファ戦略の使用開始方法が具体例とともに示されています。