显示

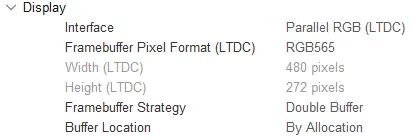

显示组包含与显示屏有关的配置,如接口、尺寸和缓冲策略。

接口与尺寸

如今,STM32微控制器可使用多种显示接口,如:

- 并行RGB(LTDC)

- MIPI DSI

- FMC

- SPI

如果MCU带有连接到LTDC或FMC的显示屏,TouchGFX Generator可生成代码,以将帧缓冲器传输到连接的显示屏。 对于DSI和SPI接口,驱动程序必须由开发人员自己实现。

Further reading

有关不同显示接口的代码具体例程,请参见场景章节。

帧缓冲像素格式

TouchGFX Generator目前支持以下帧缓冲像素格式。 当使用“Custom”显示接口时,所有选项均可用,否则选项被限制为显示屏控制器设置(例如,配置LTDC Framebuffer格式为“RGB565”时,会将TouchGFX Generator中的配置选项限制为“RGB565”)。

- BW (1bpp)

- Grey2 (2bpp)

- Grey4 (4bpp)

- ABRG2222 (8bpp)

- ARGB2222 (8bpp)

- BGRA2222 (8bpp)

- RGBA2222 (8bpp)

- RGB565 (16bpp)

- RGB888 (24bpp)

- ARGB8888 (32bpp)

- XRGB8888 (32bpp)

Note

一些像素格式没有或仅有部分ChromART(DMA2D)支持。

缓冲策略&位置

可通过TouchGFX Generator配置以下帧缓冲策略:

- 单帧缓冲 - 仅使用一个应用帧缓冲区。 可能会使性能受限,但占用内存更少。 可与“缓冲位置”配置一起使用,将其放置在内部RAM中。 为进一步优化,用户可以定义一个函数,该函数返回显示屏控制器正在处理的当前行。 该方法用于框架,以允许更新该帧期间已传输到显示屏的内存。

- 双缓冲 - 使用两个帧缓冲区。 通常以牺牲内存为代价来获得更好的性能。

- 部分缓冲- 将一个或多个用户定义的内存块作为帧缓冲区。 该策略适用于低成本解决方案,不依赖外部RAM,且显示屏的全帧缓冲可能超出可用内存。

对于单缓冲区和双缓冲区,用户可通过“缓冲器位置”来配置其位置,该配置提供以下选项:

- 按分配- 允许链接器根据链接器脚本来放置帧缓冲存储器。 默认位于内部RAM中。

- 按地址- 允许用户定义一个(单) 或两个(双) 帧缓冲地址。

部分帧缓冲策略允许用户定义以下参数:

- 块数(始终放置在内部RAM中)

- 块大小(字节)

要了解有关部分缓冲战略的一些核心概念,请阅读使用部分帧缓冲区降低内存要求的专用文章。 本文从概念上说明了如何实现部分帧缓冲,并且本文中显示的代码与TouchGFX Generator生成的代码略有不同。 有关为这些策略生成的具体示例代码,请参见帧缓冲策略。

Caution

对于STM32F7/H7:如果帧缓冲区放置在Write Through缓存存储器(例如SRAM)中,那么在DMA2D(如果已在Generator中进行配置)访问它之前,DCache会被生成的代码先清空。 记住要在STM32CubeMX中的Cortex M7的System Core设置中启用CPU Cache,这样缓存机制才能正常工作。

Further reading

如需更多关于CPU缓存的详细信息,请参阅F7和H7中的“Cache(缓存)”章节。