Display

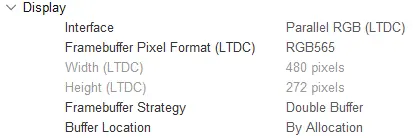

Display 그룹에는 인터페이스, 크기, 버퍼링 전략 등 디스플레이와 관련된 구성이 포함되어 있습니다.

인터페이스 및 치수

현재 STM32 마이크로컨트롤러와 함께 여러 디스플레이 인터페이스를 사용할 수 있습니다.

- 병렬 RGB (LTDC)

- MIPI DSI

- FMC

- SPI

LTDC 또는 FMC에 연결된 디스플레이가 있는 MCU의 경우, TouchGFX Generator는 프레임 버퍼를 연결된 디스플레이로 전송하는 코드를 생성할 수 있습니다. DSI 및 SPI 인터페이스 드라이버는 개발자가 직접 구현해야 합니다.

Further reading

Framebuffer Pixel Format

현재 TouchGFX Generator에서는 다음과 같은 프레임 버퍼 픽셀 형식이 지원됩니다. "Custom" 디스플레이 인터페이스를 사용할 때 모든 옵션을 사용할 수 있습니다. 그렇지 않으면 옵션이 디스플레이 컨트롤러 설정으로 제한됩니다(예: LTDC Framebuffer 형식을 "RGB565"로 설정하면 TouchGFX Generator에서 옵션이 "RGB565"로 제한됨).

- BW (1bpp)

- Grey2 (2bpp)

- Grey4 (4bpp)

- ABRG2222 (8bpp)

- ARGB2222 (8bpp)

- BGRA2222 (8bpp)

- RGBA2222 (8bpp)

- RGB565 (16bpp)

- RGB888 (24bpp)

- ARGB8888 (32bpp)

- XRGB8888 (32bpp)

Note

버퍼링 전략 및 위치

TouchGFX Generator를 통해 다음과 같은 프레임 버퍼 전략을 구성할 수 있습니다.

- Single Buffer - 하나의 애플리케이션 프레임 버퍼만 사용합니다. 성능에 제약이 있을 수 있지만, 메모리는 덜 사용합니다. "Buffer Location" 구성과 함께 사용해서 내부 RAM에 배치할 수 있습니다. 추가 최적화를 위해 사용자는 디스플레이 컨트롤러에서 처리 중인 현재 라인을 반환하는 함수를 정의할 수 있습니다. 이 메서드를 사용하면 프레임워크에서 이 프레임 동안 디스플레이로 이미 전송된 메모리에 업데이트를 허용할 수 있습니다.

- Double Buffer - 두 개의 프레임 버퍼를 사용합니다. 일반적으로 비용 대비 메모리 성능이 더 뛰어납니다

- Partial Buffer - 1개 이상의 맞춤형 메모리 청크를 프레임 버퍼로 사용합니다. 이 전략은 외부 RAM에 의존하지는 않지만ㅡ 전체 프레임 버퍼가 가용 메모리를 초과하는 디스플레이가 있는 저가 솔루션을 대상으로 합니다.

Single Buffer 및 Double Buffer의 경우, 사용자는 다음 옵션을 제공하는 "Buffer Location" 구성을 통해 위치를 설정할 수 있습니다.

- By Allocation - 링커 스크립트에 따라 링커가 프레임 버퍼 메모리를 배치하도록 합니다. 내부 RAM이 기본값입니다.

- By Address - 사용자가 1개(단일) 또는 2개(이중) 프레임 버퍼 주소를 정의할 수 있습니다.

Partial Buffer 전략을 사용하면 사용자가 다음 매개변수를 정의할 수 있습니다.

- 블록 수(항상 내부 RAM에 위치)

- 블록 크기(바이트)

Partial Buffer 전략에 관한 몇 가지 핵심 개념을 이해하려면 부분 Frame Buffer를 사용해 Lowering Memory 요구 사항과 관련된 전용 문서를 읽어보시기 바랍니다. 이 문서는 부분 프레임 버퍼를 달성하는 방법을 개념적으로 보여주는 것이기 때문에 이 문서에 나와 있는 코드는 TouchGFX Generator에서 생성된 코드와는 약간 다릅니다. 이러한 전략에 대해 생성된 코드의 구체적인 예는Frame Buffer Strategies을 참조하십시오.