マイクロコントローラ

マイクロコントローラ・ユニット(MCU)はすべての組込みソリューションのコアとなるもので、コストと機能の両面で幅広いオプションが用意されています。

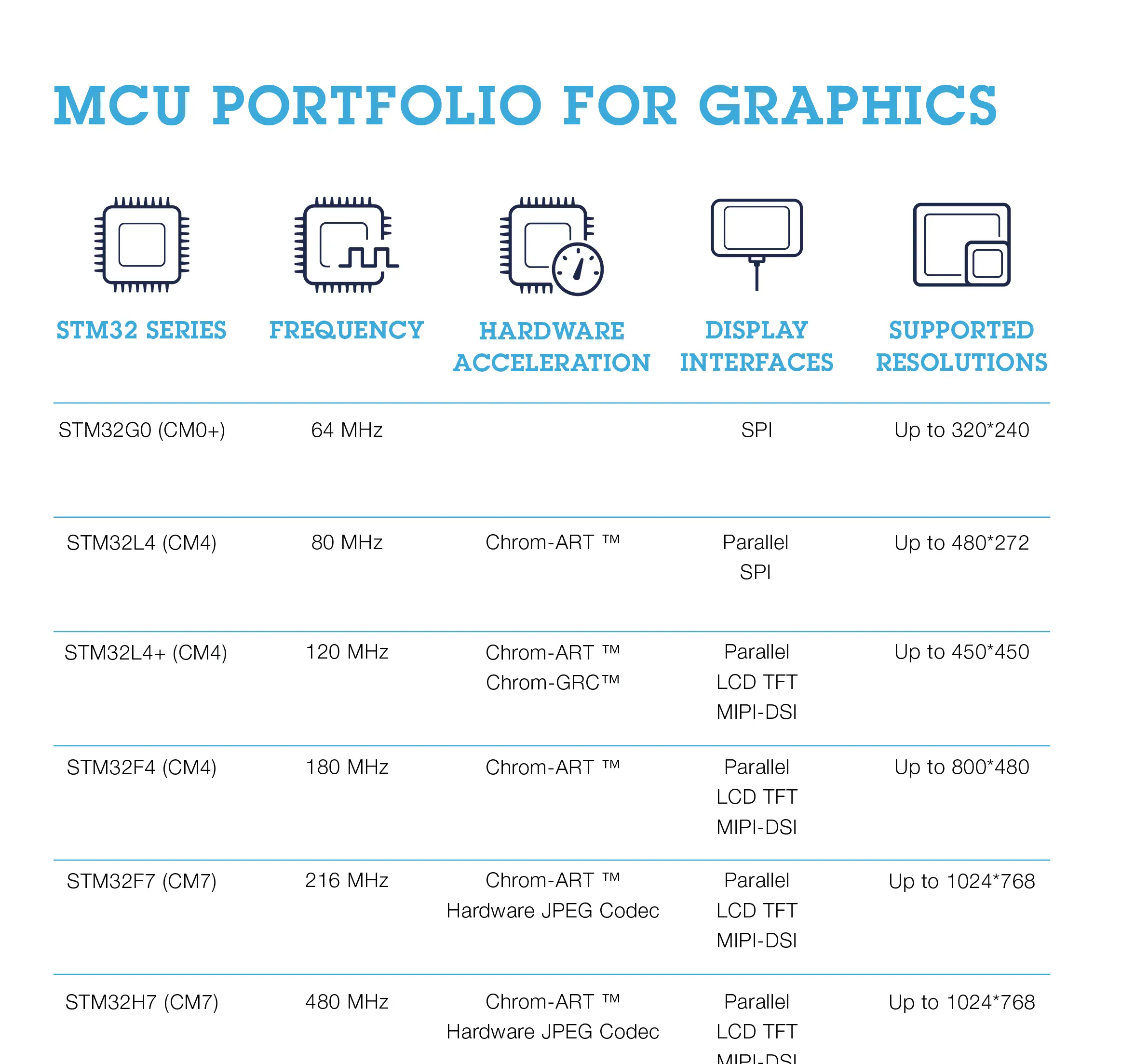

グラフィックス用のマイクロコントローラを選択する場合には、サポートされているディスプレイ・インタフェース、マイクロコントローラ・パッケージ、サイズ、達成可能なグラフィック性能を考慮する必要があります。達成可能なグラフィック性能は以下の2つの主要ポイントに左右されます。

画像合成

- マイクロコントローラに内蔵されたグラフィック・アクセラレータの可用性

- システム内のキャッシュ・メモリの可用性

メモリ・アクセスと帯域幅

- クロック周波数とサブシステムのバス周波数

- 内蔵のFlashメモリおよびRAMメモリへのアクセス

グラフィックス以外で実行されている、アプリケーションに求められる機能(モータ制御、ワイヤレスなど)を考慮することも重要です。 これらもマイクロコントローラの選定に影響します。

ここでは、さまざまなマイクロコントローラのオプションと、GUI駆動のアプリケーション用のSTM32マイクロコントローラを決定する際に考慮すべきパラメータについて説明します。

Further reading

周波数

コア周波数は、画面リフレッシュ、画面やアニメーションの滑らかな表示の面で、グラフィック・アプリケーションの性能に大きく影響します。

これは、内部または外部のメモリからディスプレイのフレームバッファに転送可能なデータ量に影響し、計算処理やアニメーションの性能にも影響します。

周波数が高いほど、特定の時間枠内で転送可能なデータ量が増え、より複雑なアニメーションが作成可能になります。

STM32製品の最大コア周波数は480MHzです。

Note

グラフィック・サブシステム周波数

コアCPU周波数とグラフィック・サブシステム周波数を区別することが重要です。 グラフィック・サブシステム周波数には、内部バスの周波数、グラフィック・アクセラレータの周波数、ならびに内部および外部メモリのアクセス・スピードが含まれます。

グラフィック・サブシステム周波数は、全体のグラフィック性能にも大きく影響します。

例

次の例では、STM32H7で内部RAMから実行する場合のコアとサブシステムの理論上の性能を評価しています。

- CPUコアは480MHzで動作している。

- 64bit AXIバスの周波数は240MHz。

- LCD-TFTディスプレイ・コントローラ(LTDC)は64bit AXIバスを使用しており、10サイクルで8回の転送を実行する。

- 内部RAMに大きな遅延は発生せず、ゼロ・ウェイト・ステートで動作。

したがって、LTDCペリフェラルがアクセスしたときの内部RAMの帯域幅は次のようになります。

- 帯域幅 = 240 MHz x 8/10 x 8バイト = 1,536MB/s

この帯域幅では、内部RAMは色深度32bpp、解像度800x480で、1000 frames/sec(fps)のデータ転送が可能となります。 通常は(ピクセル・クロックやポーチなどを調整することで)ディスプレイへの転送を60fpsに制限すると、LTDCおよび内部RAMの帯域幅はボトルネックになりません。

組込みハードウェア・アクセラレーション機能

それぞれのSTM32マイクロコントローラに多様なハードウェア・アクセラレーション機能が内蔵されており、高性能グラフィック・アプリケーションの実現を可能にしています。

Chrom-ART

Chrom-ARTは、グラフィック処理の実行を支援する高度なDMAです。 DMA2Dとも呼ばれています。

Chrom-ARTアクセラレータは、多くのSTM32プラットフォームに内蔵されており、CPUに負荷をかけることなく画像の処理や転送が可能になります。 色の塗りつぶし、画像コピー、ブレンディング、ピクセル・フォーマットの変換など、主要なグラフィック処理を加速させることができます。

Chrom-ARTアクセラレータは、2つのレイヤをブレンディングし、元のピクセル・フォーマットを目的の出力ピクセル・フォーマットに変換し、結果を保存先メモリに転送するという操作を、わずか1回の操作で実行することができます。

Chrom-ARTアクセラレータは、カラー・ルックアップ・テーブル(CLUT)によるカラー・フォーマットもサポートしています。 これによりメモリを節約することができます。

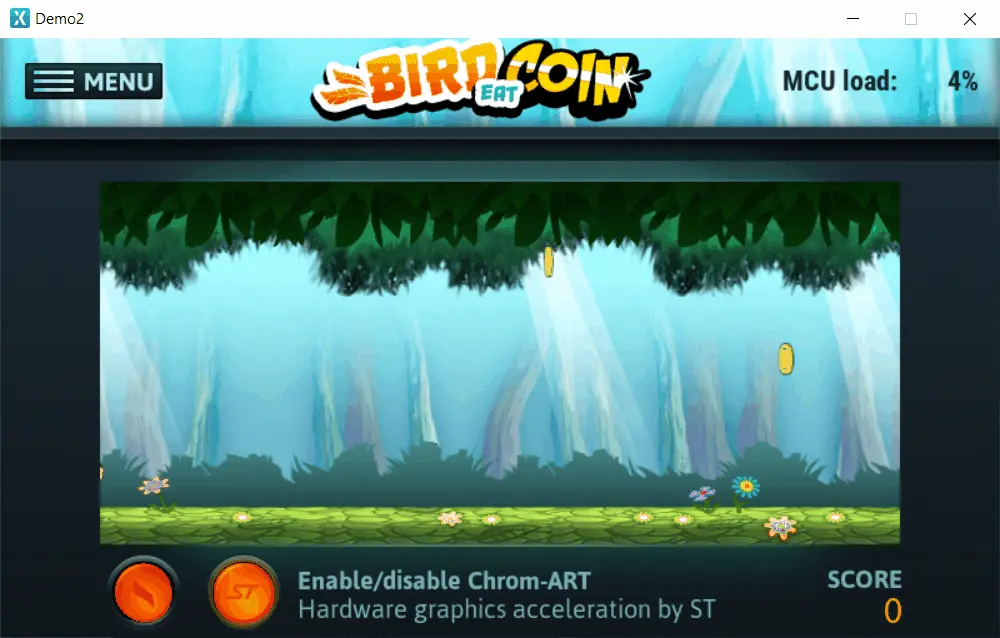

STM32F496-EVALボード上で実行したアプリケーションの例を次に示します。ここでは、Chrom-ARTを有効にするとCPU負荷が82%から4%に減少しています。

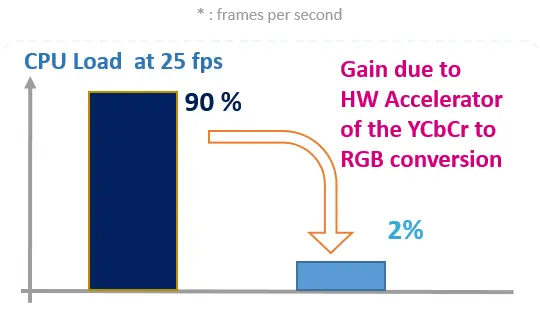

また、STM32H7では、YCbCrフォーマットからRGBフォーマットへの変換機能もChrom-ARTペリフェラルに追加されています。 この機能をJPEGハードウェア・コーデックと組み合わせることで、JPEG画像のエンコーディングおよびデコーディング時のCPUの負荷を軽減することができます。

Chrom-ARTアクセラレータは、上記の機能によって、グラフィック・アプリケーションに多大な利点をもたらします。 選択したマイクロコントローラにChrom-ARTが内蔵されている場合は、TouchGFXがすべてのChrom-ART機能を操作し、可能なすべての描画操作を(CPUではなく)Chrom-ARTペリフェラルにリダイレクトします。

Chrom-ARTペリフェラルは、高性能STM32ファミリで使用できます。

Further reading

JPEGハードウェア・コーデック

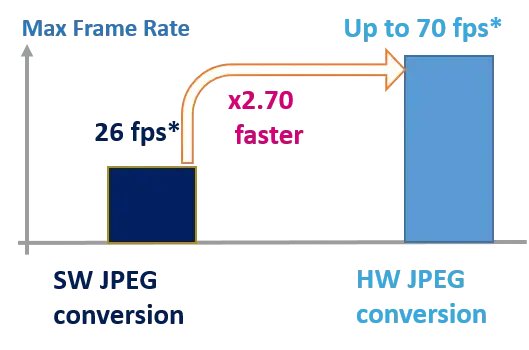

STM32H7およびSTM32F7シリーズには、画像やビデオをエンコードおよびデコードするためにJPEGハードウェア・コーデックが備わっています。

この機能は、UIアプリケーションでビデオ・ファイルを再生したりJPEG画像を表示したりする必要がある場合に、重要な役割を果たします。

一般的にJPEG画像のメモリ使用量は大きくありません。 JPEGハードウェア・コーデックでは、CPUの過負荷を招くことなく実行時に画像をデコードできます。

一部のTouchGFXデモでは、JPEGハードウェア・コーデックを利用して、MJPEGビデオ再生中のCPU負荷を軽減しています。

Further reading

Chrom-GRC

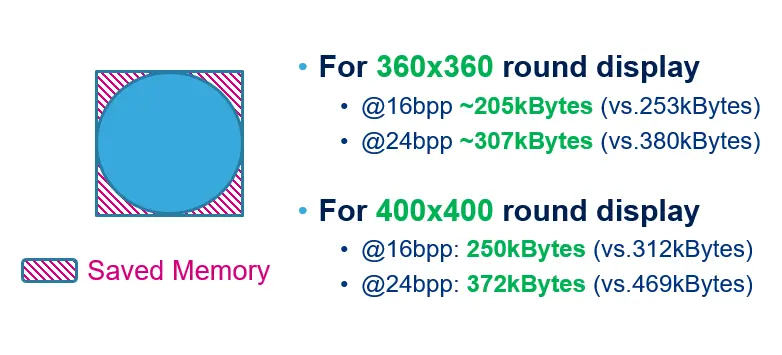

STM32 Chrom-GRC™(GFXMMU)は、いくつかのSTM32マイクロコントローラに含まれるペリフェラルであり、最近の非長方形ディスプレイへのトレンドを効率的にサポートすることを目的としています。

Chrom-GRC™ペリフェラルによりアプリケーションは、非長方形ディスプレイに対するデータ処理時にフレームバッファを保存するために必要なRAMの量を減らすことができます。

円形ディスプレイの場合、このペリフェラルによってメモリ必要量が20%削減されます。

非四角形の画面を制御する場合にChrom-GRC™ペリフェラルは必須ではありませんが、使用が推奨されます。

Further reading

内部Flash

ビットマップ・リソースを使用するグラフィカル・ユーザ・インタフェース・アプリケーションでは、データを保存するために不揮発性メモリが必要です。 内部Flashからの実行や内部Flashへのアクセスは、外部Flashに対するよりも最大で2倍高速になることがあります。

内部Flashはサイズに制限があるので、ほとんどの場合はTouchGFXフレームワーク、画面定義、UIロジックを保存するために使用され、ビットマップ・データは外部Flashに保存されています。

グラフィック・アプリケーションに使用されるSTM32製品のポートフォリオでは、数KBから数MBの範囲の内部Flashメモリが搭載されています。

ビットマップ・データ量が内部Flash内に収まりきらない場合は、外部Flashが必要になる可能性があります。

Further reading

TouchGFXのFlashメモリの必要量は以下のとおりです。

- フレームワーク: 60KB~100KB

- 画面定義およびGUIロジック: 1KB~100KB

これらの数値は、使用するフレームワーク機能とアプリケーションのサイズや複雑さによって異なります。

内部RAM

内部RAMはフレームバッファの保存に使用できますが、それはフレームバッファのサイズが使用可能なメモリ内に収まる場合です。 そうでない場合は、外部メモリを追加して設定することになります。

フレームバッファのサイズの計算は、幅、高さ、色深度に依存します。 たとえば、HVGA解像度(480x320)で16bitカラーのディスプレイの場合、1つのフレームバッファに必要なメモリは次のように計算されます。

1フレームバッファのサイズ = 480 x 320 x 2 = 307,200バイト

グラフィック・アプリケーションに使用されるSTM32製品には、数KBから数MBの範囲の内部RAMが搭載されています。

Further reading

TouchGFXのRAM必要量は以下のとおりです。

- フレームワーク: 10KB~30KB

- ウィジェット: 1KB~15KB

メモリ要件はアプリケーションごとに異なります。

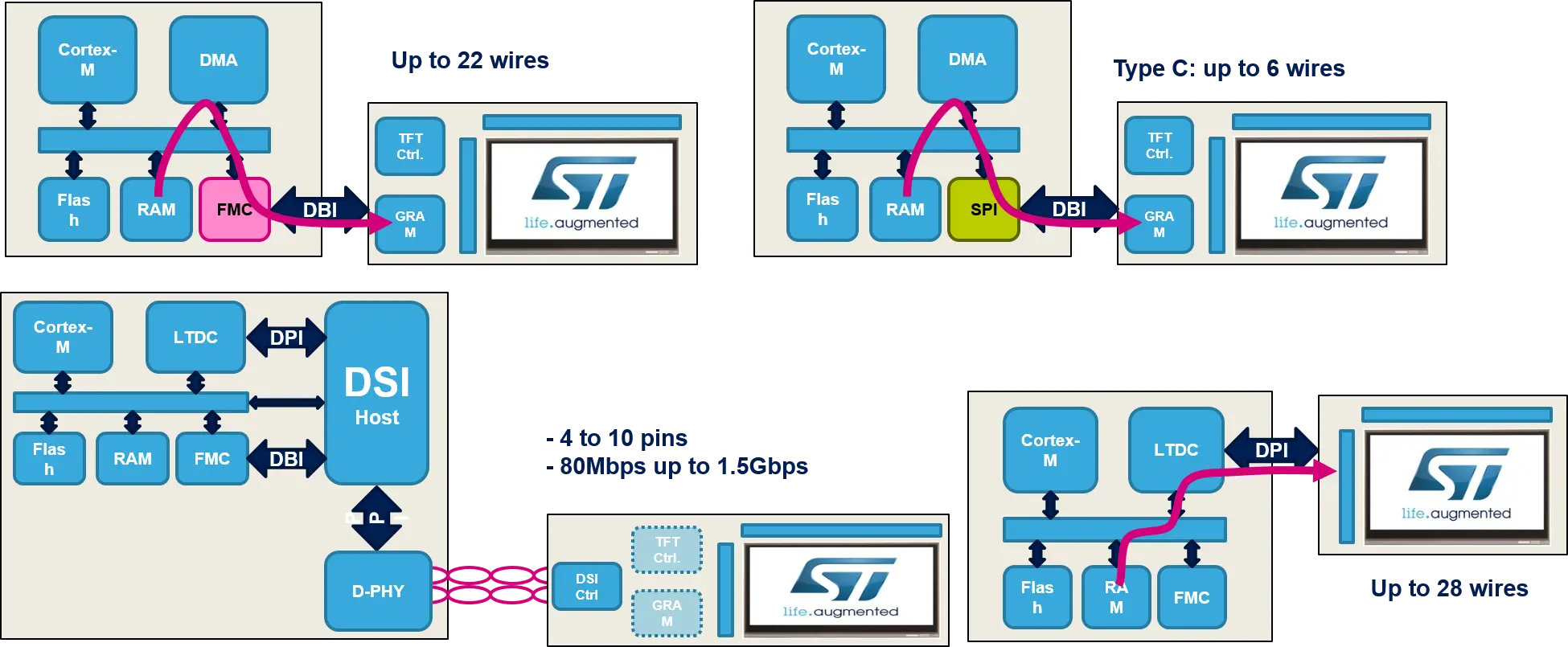

LCDコントローラ

マイクロコントローラの選択は、使用するディスプレイ・インタフェースや解像度にも依存します。 たとえば、解像度800x480は、データ転送速度の点で効率的なインタフェースでないと達成できません。 高解像度用にはRGB-TFTおよびMPI-DSIインタフェースがよく使用されます。多くの場合に、SPIまたはパラレル8080/6800よりも高帯域幅だからです。 解像度の低いディスプレイの多くはコントローラやGRAMを内蔵しているので、シンプルなSPIまたは8080/6800インタフェースを介して接続することができます。

高解像度ディスプレイ(WQVGA以上)の多くはコントローラやGRAMを内蔵していないので、マイクロコントローラ側にコントローラが必要になります。 RGB-TFTおよびMIPI DSIインタフェースを搭載したSTM32マイクロコントローラには、このコントローラを備えています。

Further reading

パッケージとI/O

必要なI/Oの数は、選択するディスプレイや外部メモリによって異なります。 パラレルRAM/Flashを使用してパラレル・ディスプレイを使用するには、多数のI/Oが必要になり、パッケージが大きくなります。

メモリ・インタフェース

マイクロコントローラの内部Flashと内部RAMの容量が十分でない場合、最適な外部メモリ・インタフェースを搭載した適切なマイクロコントローラを選択することが重要になります。 STM32製品は、NOR、NAND、SRAM、SDRAM、LPSDR SDRAM、およびPSRAMメモリとのインタフェースのために、さまざまなメモリ・コントローラ・ペリフェラルを提供しています。

フレキシブル・メモリ・コントローラ(FMC)とフレキシブル・スタティック・メモリ・コントローラ(FSMC)

スタティックRAMのサポートに加えて、FMCではダイナミックRAM(SDRAM)のサポートがFSMCに加わります。 外部アクセス・スピードが速く、8bit、16bit、特に32bitデータ・バスを備えたフレキシブル・メモリ・コントローラ(FMC)では、外部RAMとの間で高スループットが可能になり、高解像度ディスプレイを適切にサポートできるようになります。 FMCにはメモリ・バンクごとに独立したチップ選択機能があります。 FMCでは、データ用の外部Flashメモリ、フレームバッファ用の外部RAMメモリ、およびグラフィック・スタック用のヒープ拡張をコントロールできます。

シリアル・メモリ・インタフェース

STM32製品によっては、シリアル・メモリ・インタフェースが内蔵されており、QSPI、PSRAM、OPI PSRAM、およびHyper RAMと同時に、シングル、ダブル、クワッド、オクト、およびHyperBus Flashメモリとのインタフェースが可能になっているものがあります。 シリアルの高速メモリ・インタフェースは、メモリ・マップド・モードで最大256MB、インダイレクト・モードで最大4GBまでデータ転送できます。

パラレル・インタフェースと比較して、シリアル・メモリ・インタフェースでは低コストの外部Flashメモリとの接続が可能となるので、パッケージが小型化し、使用するピン数が少なくなります。

Further reading

STM32バリュー・ライン製品

価格を最適化するために、STM32H7およびSTM32F7プラットフォームでは、内部Flashのサイズが限定されたバリュー・ライン製品が提供されています。 これらの製品では、グラフィック・リソースは外部Flashに保存されます。

Cortex®-Mコア

STM32マイクロコントローラは、さまざまなArm® Cortex®-Mアーキテクチャで提供されています。 STM32でグラフィックスを実行する場合に、最もよく使用されるコアを以下に示します。

Cortex®-M0+

Cortex®-M0+はシンプルなアーキテクチャと低価格を特徴としています。 小規模の静的なグラフィック・アプリケーションを低解像度で実行する場合にお勧めします。

Cortex®-M4

Cortex®-M4にはM0+よりも多くの機能が含まれており、計算速度も上がります。 DSP命令セットと単精度の浮動小数点ユニット(FPU)が含まれています。 これらの命令はCPUの負荷を軽減し、計算速度を向上させます。

Cortex®-M7

Cortex®-M7にはさらに複雑なアーキテクチャとDSP命令セットが含まれており、倍精度の高効率なFPUと、データおよび命令用の最大16KBのレベル1キャッシュ・メモリが搭載されています。 このキャッシュ・メモリにより、データや命令コードを計算ユニットの近くに配置してフェッチ時間を最適化できるようになります。

機能の概要

| 機能 | Cortex-M0+ | Cortex-M4 | Cortex-M7 |

|---|---|---|---|

| DMIPS/MHzの範囲 | 0.95~1.36 | 1.25~1.95 | 2.14~3.23 |

| Core Mark®/MHz | 2.46 | 3.42 | 5.01 |

| デジタル信号処理(DSP)拡張 | なし | あり | あり |

| 浮動小数点ハードウェア | なし | あり(SP) | あり(SP + DP) |

| 内蔵キャッシュ | なし | なし | あり(オプション4KB~64KB)I-Cache D-Cache |

| バス・プロトコル | AHB Lite、高速I/O | AHB Lite、APB | AXI4、AHB Lite、APB、TCM |

| デュアル・コア・ロックステップのサポート | なし | なし | あり |

レベル1キャッシュ:

STM32H7およびSTM32F7シリーズには、命令およびデータ用の最大16KBのL1キャッシュが含まれています。 L1キャッシュは、データまたは命令のセットをCPUの近くに保存するので、CPUは繰り返し使用する同じデータをフェッチし続ける必要がなくなります。

Further reading

デュアル・コア

STM32H7シリーズには以下のデュアル・コア・ラインが含まれています。

Arm® Cortex®-M7コア(最大480MHz)とCortex®-M4コア(最大240MHz)によって、極めて優れた処理性能およびアプリケーション・パーティショニングを実現します。 デュアル・コアのSTM32H7製品ラインにはSMPSが内蔵されており、ダイナミック・パワー効率が向上します。

2つ目のCortex®-M4によって計算負荷を軽減できるので、M7コアを描画やグラフィック処理用に開放することができます。

Note

バス・アーキテクチャ

ほとんどのSTM32マイクロコントローラは、すべてのマスタ(CPU、DMAなど)とスレーブ(Flashメモリ、RAM、FSMC、AHBおよびAPBペリフェラル)を相互接続する32bitマルチAHBバス・マトリックスを提供しています。 これにより、複数の高速ペリフェラルが同時動作する場合でも、シームレスで効率的な動作が確保されます。

マルチAHBの相互接続に加えて、一部のSTM32(Cortex®-M7)製品は帯域幅を広げるために64bit AXIを内蔵しています。 これにより性能と消費電力の最適なバランスが得られます。

価格

内部Flashや内部RAMの容量やパッケージ内で使用可能なピン数が、マイクロコントローラの価格に影響します。 インタフェース、解像度、性能などの要件を検討して、最終的には最適なマイクロコントローラを選択し、価格を見積もることができます。