STM32H7R7/S7图形处理性能

本文探讨了STM32H7R/S系列MCU的特殊架构,以及其在图形处理应用中需注意的关键事项。 但大部分技术要点同样适用于所有需要外接RAM和Flash的STM32 MCU。

鉴于STM32H7R/S属于高性能MCU,本文并非关于如何创建TouchGFX开发板设置 (TBS) 的入门指南。 本文仅深入探讨STM32H7R/S特有的关键技术领域。 有关如何创建TouchGFX TBS的通用指南,请参见驱动板卡指南。

有关STM32H7R7/S7的更多信息,请访问产品页面或查看包含完整STM32H7RSYouTube演示研讨会的YouTube专题列表。

TouchGFX Designer已集成STM32H7S78开发板的TBS支持包,该包提供了在STM32H7R/S上运行TouchGFX的完整示例项目。 开发人员可直接将此TBS作为STM32H7R/S TouchGFX应用开发的参考模板。 该项目基于STM32CubeMX构建,通过打开STM32H7S78-DK.ioc文件即可获得缓存、MPU、外部存储器等的推荐配置。

存储器配置方案

STM32H7R/S是一款bootflash MCU。 带bootflash的MCU是指内置小型Flash用于存储自举程序的微控制器,主应用程序及相关资源则存储在外部存储器中。 STM32H7R/S还集成620 KB嵌入式SRAM。 因此,STM32H7R/S在图形处理应用中,需同时使用外部RAM和Flash。 由于外部存储器工作频率通常仅为CPU频率的1/2或1/3,其带宽往往成为系统瓶颈。 对于STM32H7R7/S7,其两个XSPI接口(16位和8位)在双倍传输速率模式下最高可运行至200 MHz,而FMC接口(16位或32位)的最高运行频率为100 MHz。

外部存储器管理器

STM32CubeMX在“分类 → 中间件和软件包”目录下提供了“外部存储器管理器”和“外部存储器加载器”两个工具。 这些工具旨在协助开发者在bootflash或无Flash应用场景下完成外部存储器的配置工作。 这些工具能够显著简化外部加载器的创建流程,并提供应用程序类型选择等便捷功能。 有关工具的使用详情见此处。 此外,ST即将发布技术文章“STM32外部串行存储器简介”。

Further reading

外部RAM中的帧缓存

在外部RAM中配置帧缓存时,内存带宽需求与限制是需要首要考虑的关键因素。 由于显示屏未集成GRAM,系统必须持续按照显示屏指定的刷新率传输帧缓存数据。 探索套件所配显示屏的刷新率为60 Hz。 这将导致外部RAM接口的大部分带宽被LTDC的帧缓存更新操作占用。 LTDC的带宽需求可通过以下公式计算:

像素时钟 (LCD_CLK) = 总屏幕像素数 × 刷新率

单个LTDC层带宽需求 = LCD_CLK × Bpp

此外,DMA2D和GPU2D在帧缓存上执行操作时也需占用外部RAM带宽。 若内存同时用于其他用途(如运行应用程序代码),可用带宽将进一步受限。

这些因素叠加会导致外部RAM总线过载。

在此阅读文章,了解在外部RAM中运行带有帧缓存的图形时的注意事项。

如需详细了解LTDC显示接口及外部RAM帧缓存的限制条件与技术要点,请参见“LTDC应用笔记”。 建议重点关注第5章“基于LTDC的图形应用程序开发”和第7章“LTDC应用示例”。

若外部RAM带宽已达极限,请参考第5.5.2节“外部存储器帧缓存读取优化”及第5.5.3节“SDRAM帧缓存读取优化”。

Further reading

紧耦合存储器

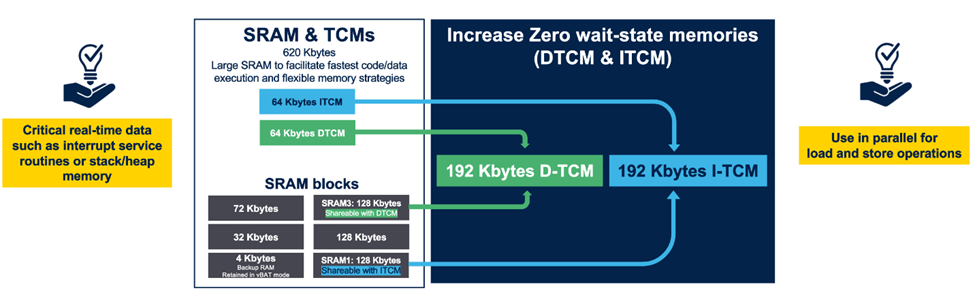

STM32H7R/S Cortex-M7支持64位宽零等待周期直接访问紧耦合存储器 (TCM)。 该架构可提供多达192 KB的数据TCM (DTCM) 和指令TCM (ITCM) 容量。 ITCM和DTCM分别是数据读写与指令提取的最佳存储区域。 因此,ITCM应被用于执行确定性极高的关键代码,例如不能等待缓存失效的中断处理程序,以及关键控制循环等场景。 在使用RTOS的实时应用中,堆通常会被高频使用。 因此建议将RTOS的栈和堆分配至DTCM。 若有剩余空间,全局变量亦可存放于此区域。

需特别注意,ITCM和DTCM会占用SRAM1和SRAM3的部分内存空间。 这意味着启用ITCM和DTCM时,内部SRAM的可用容量会减少。

与其他H7系列MCU相同,STM32H7R/S配备一级 (L1) 缓存。 有关L1缓存的详细信息,请参见“H7缓存应用笔记”。 请重点参考第4章:“常见误区与优化建议”。

关于外部SPI存储器的配置详情,请参考“OSPI、HSPI及XSPI接口应用指南”。

Further reading

应用程序类型

在启动过程中,自举程序会根据所选应用程序类型执行不同操作。 它既可以指向外部Flash中已存在的应用程序,也可以将应用程序加载到另一内存(通常是外部RAM)中。

执行外部Flash中已存在的应用程序称为就地执行 (XiP)。 在启动过程中将应用程序从Flash复制到RAM,再从RAM执行的操作称为加载运行 (LRUN)。

若应用程序已加密,则只能使用LRUN。 有关STM32加密的更多信息,请参见加密应用笔记。

Further reading

就地执行 (XiP)

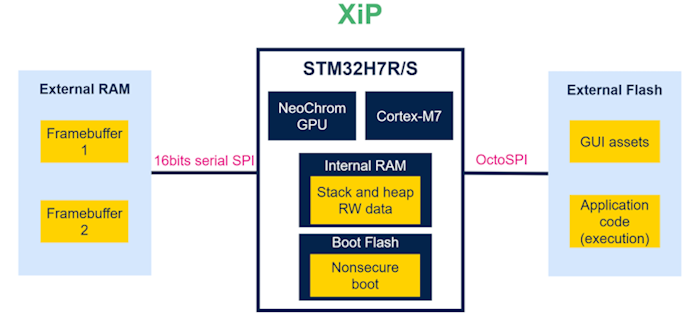

下图以图形应用程序为例展示XiP的内存布局。 XiP为默认应用类型。

如XiP示意图所示,外部Flash通过OctoSPI接口同时提供应用程序代码和图形资源的访问。 CPU持续访问应用代码,可能导致NeoChrom GPU或Chrom-ART访问资源时出现延迟。 这会显著影响图形处理性能。 为缓解此问题,强烈建议运行XiP时启用外部Flash的指令缓存功能。 如此可实现重复指令直接从缓存而非外部Flash读取,从而减轻带宽负载并提升外部Flash接口访问效率。

加载运行 (LRUN)

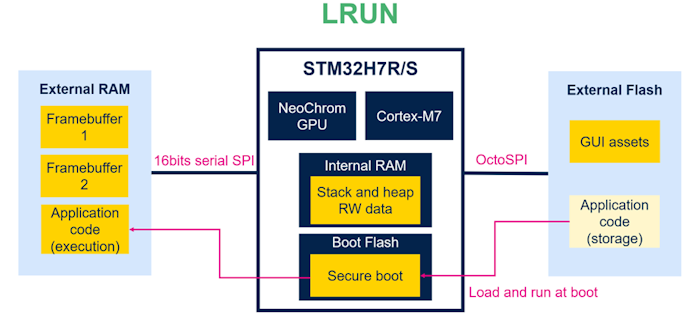

下图展示了图形应用中LRUN模式的对应示例。

如LRUN示意图所示,应用程序代码与图形资源实现了物理分离,从而改善了资源访问效率。 但同时也意味着外部RAM接口将承担更大负载,因为访问帧缓存和应用程序代码都需要该接口。 在此配置下,强烈建议启用外部RAM接口的指令缓存功能。

在STM32H7R/S上采用LRUN模式运行图形应用时,需重点关注以下性能优化事项:

首先,建议将位图、字体等资源保留在外部Flash中。 由于资源会被频繁访问,将其存储在外部RAM中会显著增加外部RAM的带宽负载。 此外,图形资源通常无需加密处理。

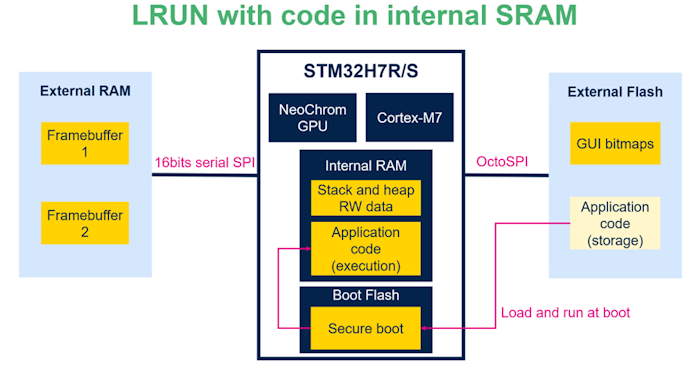

其次,如下图所示,建议评估将应用程序代码存入内部SRAM的可行性。 由于内部总线的传输速率更高,相较于将应用程序代码存储在外部Flash或RAM中,从内部SRAM访问和执行速度更快。 STM32H7R/S连接内部SRAM的AXI总线运行速度可达300 MHz。 此外,该配置允许将图形资源、帧缓存和应用程序代码分别存储于三个独立区域,从而将带宽负载分散到三条独立总线。

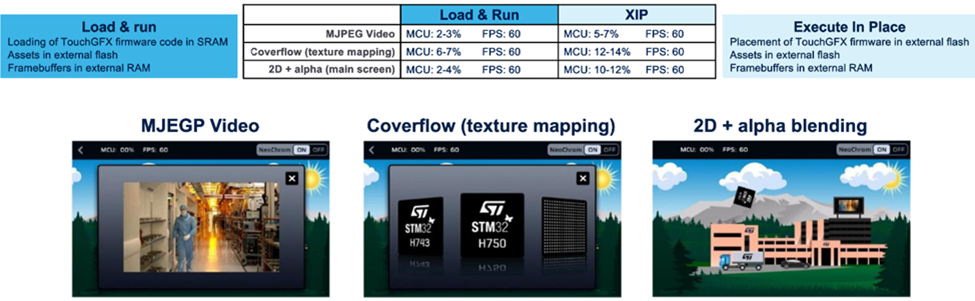

性能比较

以下分别展示了采用XiP和LRUN模式的复杂GUI应用案例。 LRUN应用程序的应用代码存储在内部SRAM中。 比较结果表明不同配置对MCU负载的影响机制。 通过将TouchGFX框架和应用程序置于内部SRAM,减少了从外部RAM和Flash中获取数据所需的周期数,从而有效降低MCU负载。

参考模型为STM32H7S78-DK开发板预装演示程序。

比较结果表明,当应用代码置于内部SRAM时MCU负载会降低。 与XiP相比,采用LRUN模式MCU负载可减少约50%。

比较结果表明,当应用代码置于内部SRAM时MCU负载会显著降低。 这是由于内部SRAM相比外部RAM和Flash具有更快的访问速度。 相较于XiP模式,采用LRUN运行模式并结合内部SRAM存储应用代码可使MCU负载减少50%。 将应用代码存储于内部SRAM的LRUN方案可提供最佳性能。 但该配置仅在应用代码容量适配可用内部SRAM时才可行。

MPU 配置

内存保护单元 (MPU) 用于保护存储区域,防止非预期的内存访问和执行操作。

在Arm® Cortex®-M7处理器上,必须防止对外部存储器的推测性访问,否则可能引发高延迟或系统错误。 对于STM32H7R/S,这将影响访问内存的AXI主设备,并显著降低图形性能。

MPU可通过控制可访问的地址范围来防止推测性读取访问。 最简单的方法是使用包含整个内存区域的背景区域,通过将其设置为“强排序,永不执行”来限制访问。

背景区域应定义在默认区域ID-1中,因为所有其他区域的优先级都将高于此区域。 然后,应为需要访问的内存区域定义具有相应设置的其他MPU区域。 在STM32H7R/S上最多可定义16个区域。

STM32H7S78 DK TBS的MPU配置如下。 此配置可用作参考。

| 区域0 | 全部 | 注 |

|---|---|---|

| 属性 | 值 | |

| MPU区域基址 | 0x0 | |

| MPU区域大小 | 4 GB | 覆盖MCU的整个内存区域 |

| MPU子区域禁用 | 0x0 | |

| MPU TEX字段级别 | 0级 | |

| MPU访问权限 | 禁止所有访问 | 限制所有访问操作 |

| MPU指令访问 | DISABLE | |

| MPU可共享权限 | ENABLE | |

| MPU可缓存权限 | DISABLE | |

| MPU可缓冲权限 | DISABLE |

| 区域1 | 外部Flash | 注 |

|---|---|---|

| 属性 | 值 | |

| MPU区域基址 | 0x70000000 | XSPI2(外部Flash)的基址 |

| MPU区域大小 | 128 MB | 板载128 MB外部Flash |

| MPU子区域禁用 | 0x0 | |

| MPU TEX字段级别 | 1级 | |

| MPU访问权限 | 允许所有访问 | |

| MPU指令访问 | DISABLE | |

| MPU可共享权限 | DISABLE | |

| MPU可缓存权限 | ENABLE | |

| MPU可缓冲权限 | ENABLE |

| 区域2 | 外部Flash | 注 |

|---|---|---|

| 属性 | 值 | |

| MPU区域 | 使能 | |

| MPU区域基址 | 0x70000000 | XSPI2(外部Flash)的基址 |

| MPU区域大小 | 0x90000000 | 外部Flash前2 MB区域的属性配置(存放应用程序代码)将被覆盖 |

| MPU子区域禁用 | 0x0 | |

| MPU TEX字段级别 | 1级 | |

| MPU访问权限 | 允许所有访问 | |

| MPU指令访问 | ENABLE | |

| MPU可共享权限 | DISABLE | |

| MPU可缓存权限 | ENABLE | |

| MPU可缓冲权限 | ENABLE |

| 区域3 | 外部PSRAM | 注 |

|---|---|---|

| 属性 | 值 | |

| MPU区域基址 | 0x90000000 | XSPI1(外部PSRAM)的基址 |

| MPU区域大小 | 32 MB | 板载32 MB外部PSRAM |

| MPU子区域禁用 | 0x0 | |

| MPU TEX字段级别 | 1级 | |

| MPU访问权限 | 允许所有访问 | |

| MPU指令访问 | DISABLE | |

| MPU可共享权限 | DISABLE | |

| MPU可缓存权限 | DISABLE | |

| MPU可缓冲权限 | DISABLE |

| 区域4 | DTCM | 注 |

|---|---|---|

| 属性 | 值 | |

| MPU区域基址 | 0x20000000 | DTCM的基址 |

| MPU区域大小 | 64 kB | 默认64 kB DTCM配置 |

| MPU子区域禁用 | 0x0 | |

| MPU TEX字段级别 | 1级 | |

| MPU访问权限 | 允许所有访问 | |

| MPU指令访问 | DISABLE | |

| MPU可共享权限 | DISABLE | |

| MPU可缓存权限 | DISABLE | 禁用DTCM缓存,因其无法提升性能表现 |

| MPU可缓冲权限 | DISABLE |

| 区域5 | SRAM | 注 |

|---|---|---|

| 属性 | 值 | |

| MPU区域基址 | 0x24000000 | SRAM1的基址 |

| MPU区域大小 | 512 kB | 覆盖SRAM1、SRAM2、SRAM3和SRAM4 |

| MPU子区域禁用 | 0x0 | |

| MPU TEX字段级别 | 1级 | |

| MPU访问权限 | 允许所有访问 | |

| MPU指令访问 | DISABLE | |

| MPU可共享权限 | ENABLE | |

| MPU可缓存权限 | ENABLE | |

| MPU可缓冲权限 | ENABLE |

| 区域6 | GPU2D命令列表 | 注 |

|---|---|---|

| 属性 | 值 | |

| MPU区域基址 | 0x2406e000 | NeoChrom GPU命令列表置于此区域 |

| MPU区域大小 | 16 kB | 使用TouchGFX时的NeoChrom GPU命令列表默认大小(定义于nema_hal.c文件)。 |

| MPU子区域禁用 | 0x0 | |

| MPU TEX字段级别 | 0级 | |

| MPU访问权限 | 允许所有访问 | |

| MPU指令访问 | DISABLE | |

| MPU可共享权限 | ENABLE | |

| MPU可缓存权限 | DISABLE | 禁用命令列表缓存 |

| MPU可缓冲权限 | ENABLE |

有关图形专用MPU的一般配置提示,请参见LTDC应用笔记的第5.6.2节:“配置内存保护单元 (MPU)”。

如需进一步参考建议,请参见MPU应用笔记。 请重点关注第3章:“Cortex-M0+/M3/M4/M7内存类型、寄存器和属性”以及第6章:“基于STM32Cube HAL的Armv6和Armv7架构MPU设置示例”。

调试

关于在STM32CubeIDE(集成开发环境中)调试STM32H7R/S的完整指南,请参见TouchGFX Designer中TBS包内的readme文件。

由于STM32H7S78-DK的TBS自举程序和应用程序结构,在IDE中调试代码可能较为复杂。 请按以下步骤在STM32CubeIDE中调试TouchGFX应用程序:

- 在TouchGFX Designer中生成代码

- 在STM32CubeIDE中打开项目

- 启动Boot项目的调试会话

- 等待编译和烧录完成

- 终止调试会话 (Ctrl + F2)

- 启动Appli项目的调试会话

- 等待编译和烧录完成

- 点击“Resume”(F8)

- 按下STM32H7S78-DK板载的黑色NRST按钮

- 此时应用程序应停在Appli工程main() 函数首行断点处。 如未暂停,请再次点击“Resume”(F8)

- 通过“Resume”(F8) 或“Step Over”(F6) 等操作继续调试

有关调试的更多信息,请参考维基页面“STM32H7RS的DA访问入门指南”。

Further reading

图形应用程序开发结论与通用建议

如上所述,在开发STM32H7R/S图形应用程序时需考虑多项因素。 若能充分重视这些要点,凭借其高速CPU和强大的GPU2D,仍可实现卓越的图形性能。

首先需重点关注外部存储器总线的带宽限制。 虽然所有外接RAM和Flash的MCU都需关注这一点,但由于STM32H7R/S的bootflash结构,这一点尤为关键。

将关键指令和数据置于ITCM与DTCM内存可显著提升性能。

同时启用Arm® Cortex®-M7处理器内置的L1指令/数据缓存以增强性能。

根据应用需求选择XiP或LRUN运行模式,但需注意内存带宽。 若应用代码可完全装载到内部SRAM,LRUN将提供最佳性能。

必须避免推测性读取访问,因为这可能导致性能显著下降。 需对所有内存区域配置适当的MPU保护。